A) ![]()

B) ![]()

C) ![]()

D) ![]()

F) All of the above

Correct Answer

verified

Correct Answer

verified

True/False

Most sequential circuits contain a combinational logic section and a memory section.

B) False

Correct Answer

verified

Correct Answer

verified

Multiple Choice

Which of the following statements is true?

A) Asynchronous events are controlled by a clock.

B) Synchronous events do not need a clock to control them.

C) Only asynchronous events need a control clock.

D) Asynchronous events occur independently of the circuit clock.

F) A) and B)

Correct Answer

verified

Correct Answer

verified

Multiple Choice

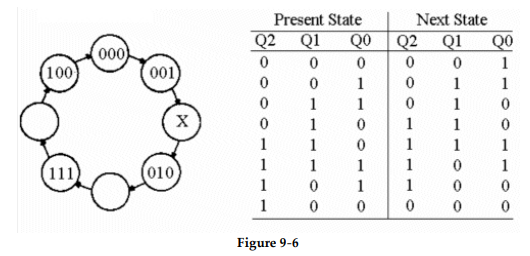

-The table shown in Figure 9- 6 is called a ________ .

-The table shown in Figure 9- 6 is called a ________ .

A) sequential truth table

B) present state table

C) state diagram

D) next- state table

F) A) and D)

Correct Answer

verified

Correct Answer

verified

True/False

The output from a Mealy state machine depends on its internal state and on external inputs.

B) False

Correct Answer

verified

Correct Answer

verified

Multiple Choice

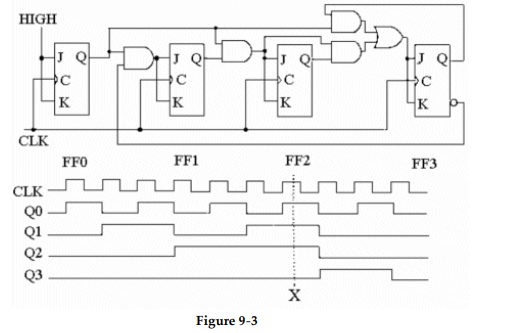

-Referring to the waveforms in Figure 9- 3, what is the decimal count at point 'X'?

-Referring to the waveforms in Figure 9- 3, what is the decimal count at point 'X'?

A) 7

B) 0110

C) 4

D) 11

F) A) and C)

Correct Answer

verified

Correct Answer

verified

True/False

The dot extension .CLK is used to indicate that the register device is a clocked flip- flop.

B) False

Correct Answer

verified

True

Correct Answer

verified

True/False

Counters are generally decoded in order to determine their count state.

B) False

Correct Answer

verified

Correct Answer

verified

Multiple Choice

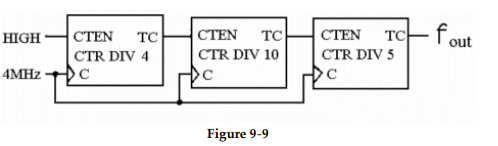

-What is the modulus of the counter shown in Figure 9- 9?

-What is the modulus of the counter shown in Figure 9- 9?

A) 0.005

B) 5000

C) 19

D) 200

F) A) and B)

Correct Answer

verified

Correct Answer

verified

Multiple Choice

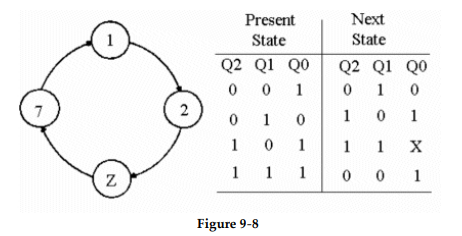

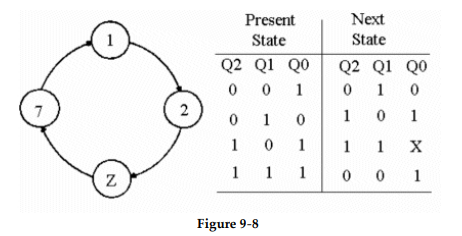

-Refer to Figure 9- 8. What value should 'X' represent in the state table?

-Refer to Figure 9- 8. What value should 'X' represent in the state table?

A) 1

B) 0

D) undefined

Correct Answer

verified

Correct Answer

verified

True/False

A Moore state machine does not have a clock input.

B) False

Correct Answer

verified

False

Correct Answer

verified

True/False

The term synchronous as applied to counter operations means that the counter is clocked so that each flip- flop in the counter is triggered at the same time.

B) False

Correct Answer

verified

Correct Answer

verified

True/False

A state machine has a finite number of states that occur in random order.

B) False

Correct Answer

verified

Correct Answer

verified

Multiple Choice

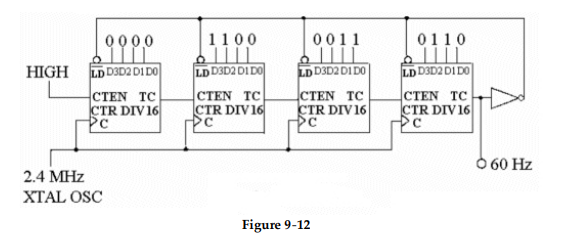

-One of the most common and least expensive crystals available is the 3.58 MHz crystal used in color television sets. What hex value would have to be loaded into the counter in Figure 9- 12 in order to use the 3.58 MHz crystal to derive the 60Hz reference signal for the clock?

-One of the most common and least expensive crystals available is the 3.58 MHz crystal used in color television sets. What hex value would have to be loaded into the counter in Figure 9- 12 in order to use the 3.58 MHz crystal to derive the 60Hz reference signal for the clock?

A) E912

B) 63C0

C) 16ED

D) E3C0

F) C) and D)

Correct Answer

verified

Correct Answer

verified

Multiple Choice

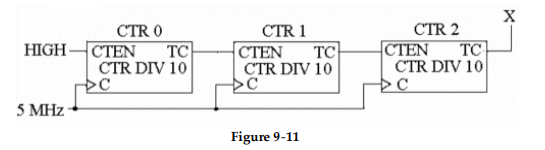

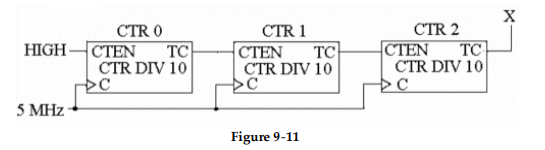

-Refer to Figure 9- 11. The TC output of CTR0 shorts to ground; what will be the output frequency at 'X'?

-Refer to Figure 9- 11. The TC output of CTR0 shorts to ground; what will be the output frequency at 'X'?

A) 50 kHz

B) 0 Hz

C) 500 kHz

D) 5 kHz

F) A) and D)

Correct Answer

verified

Correct Answer

verified

Multiple Choice

-Refer to Figure 9- 11. The output of the counter is checked and found to be 50 kHz. Is the counter working correctly? If not, what could be wrong?

-Refer to Figure 9- 11. The output of the counter is checked and found to be 50 kHz. Is the counter working correctly? If not, what could be wrong?

A) The counter is defective; there is probably a bad connection on the CTEN terminal of CTR0.

B) The counter is defective; an open exists somewhere between TC of CTR0 and CTEN of CTR1.

C) The counter is working correctly.

D) The counter is not working correctly; the TC of CTR1 is probably shorted to ground.

F) None of the above

Correct Answer

verified

B

Correct Answer

verified

Multiple Choice

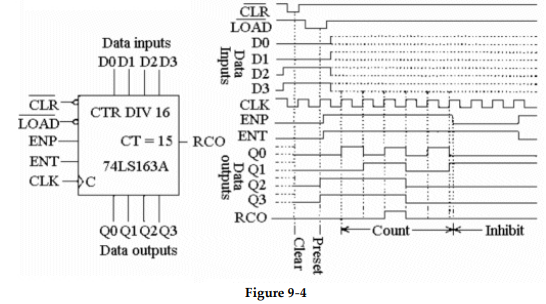

-Which of the following statements is correct concerning Figure 9- 4?

-Which of the following statements is correct concerning Figure 9- 4?

A) Both the ENP and ENT terminals must be HIGH in order for the counter to cycle on the leading edge of the CLK input.

B) Both the active- LOW CLR and LOAD inputs must be LOW in order for the counter to cycle.

C) When the CLK input goes HIGH, the data on the DATA INPUT terminals is passed through to the DATA OUTPUT terminals.

D) The active- HIGH ENT and ENP inputs must be HIGH, while the active- LOW CLR and LOAD inputs must be LOW in order for the counter to cycle.

F) All of the above

Correct Answer

verified

Correct Answer

verified

Multiple Choice

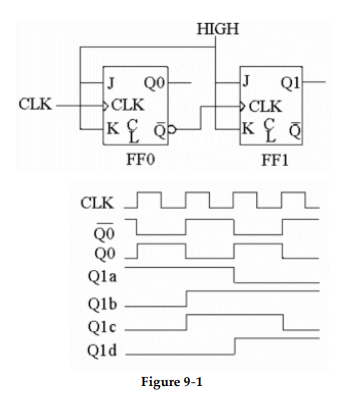

-An oscilloscope indicates that the circuit in Figure 9- 1 has no Q1 output signal. All J- K inputs are HIGH, the CLK signal is present and Q0 is toggling. The C input of FF1 is a constant LOW. What could be causing the problem?

-An oscilloscope indicates that the circuit in Figure 9- 1 has no Q1 output signal. All J- K inputs are HIGH, the CLK signal is present and Q0 is toggling. The C input of FF1 is a constant LOW. What could be causing the problem?

A) The Q0 output should be connected to the J input of FFl.

B) The input of FF1 may be shorted to ground.

C) The output of FF0 may be shorted to ground.

D) The problem could be caused by either B or C.

F) A) and C)

Correct Answer

verified

Correct Answer

verified

Multiple Choice

-What value does 'Z' represent in Figure 9- 8?

-What value does 'Z' represent in Figure 9- 8?

A) 111

B) 3

C) 5

D) 4

F) C) and D)

Correct Answer

verified

Correct Answer

verified

Multiple Choice

Which type of state machine has a clock input?

A) Moore

B) State machines do not have clock inputs.

C) Mealy

D) Moore and Mealy

F) None of the above

Correct Answer

verified

Correct Answer

verified

Showing 1 - 20 of 50

Related Exams